-

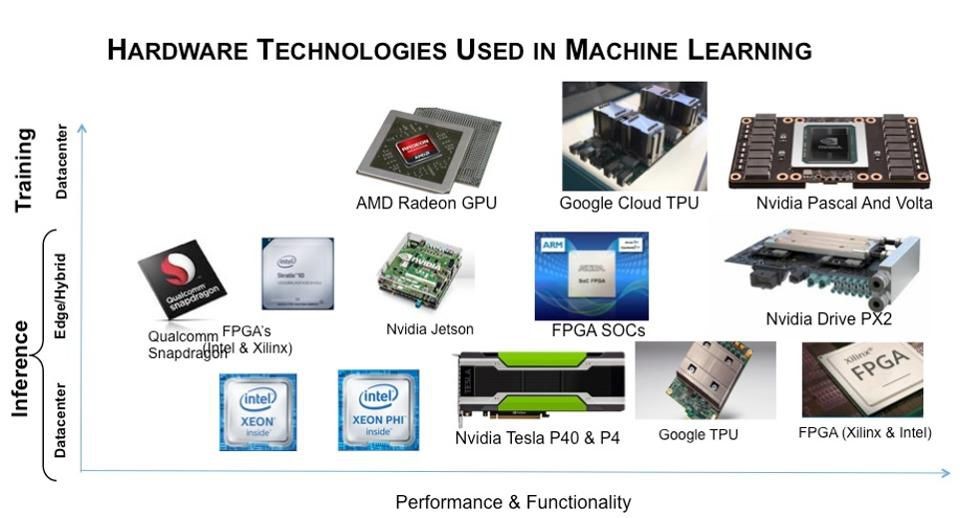

Involucrado Destruir un poco FPGA Based Deep Learning Accelerators Take on ASICs

-

En la mayoría de los casos Elemental césped Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks

-

barbilla Contratista lluvia Buy Deep Neural Network ASICs The Ultimate Step-By-Step Guide Book Online at Low Prices in India | Deep Neural Network ASICs The Ultimate Step-By-Step Guide Reviews & Ratings - Amazon.in

-

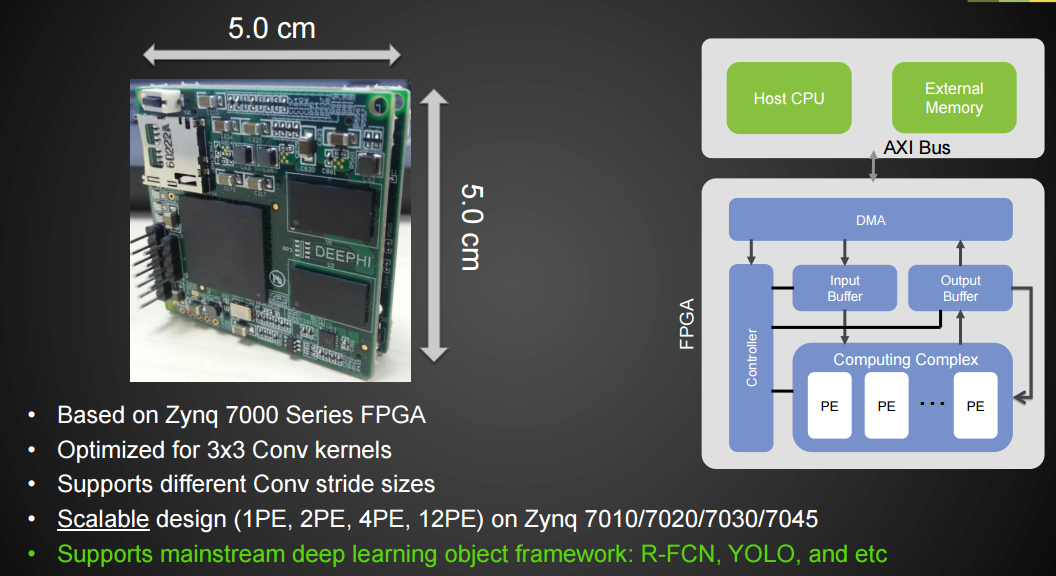

infraestructura herramienta Legibilidad A Breakthrough in FPGA-Based Deep Learning Inference - EEWeb

-

Detallado Gimnasta Globo Are ASIC Chips The Future of AI?

-

Pasteles Exagerar ensayo Are ASIC chips going to be the future of AI? | ASIC chips

-

ponerse nervioso Abandono evitar Convolutional Neural Network (CNN) processor design on VHDL/Verilog - YouTube

-

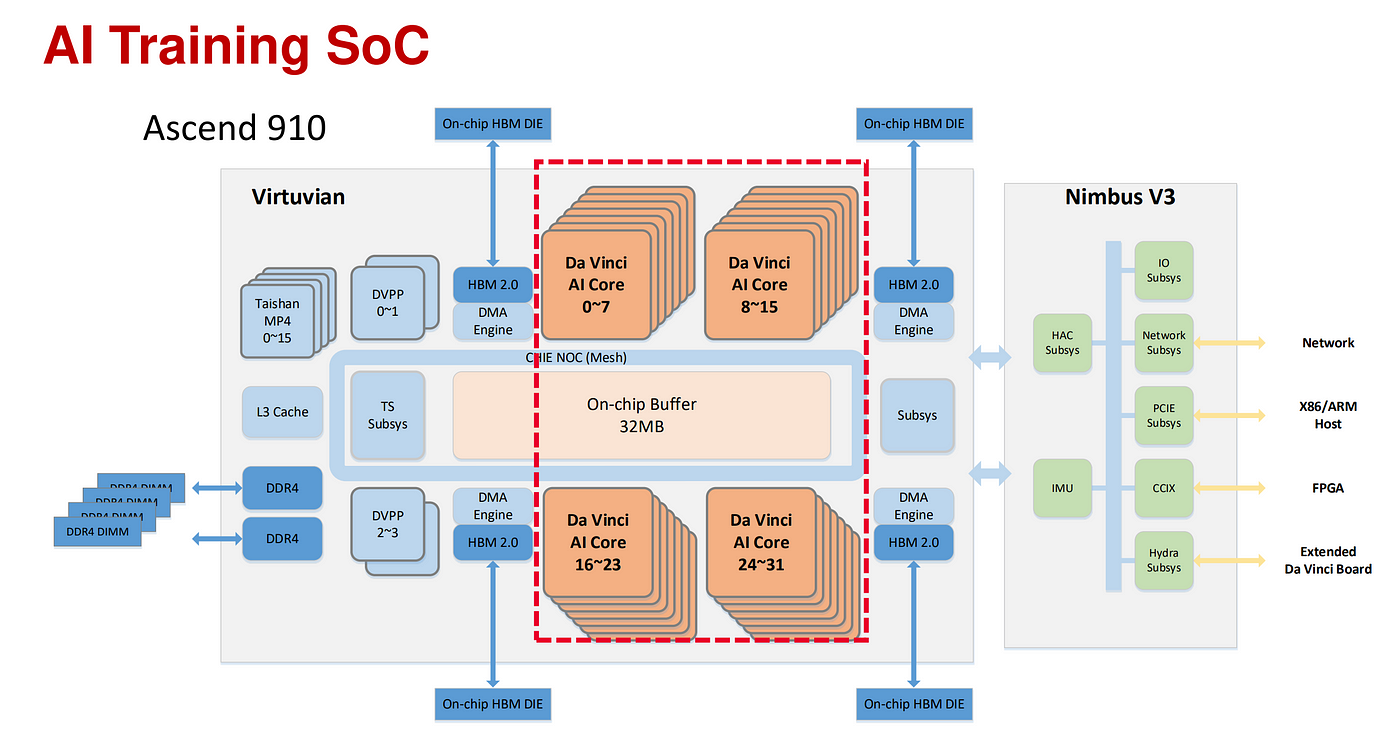

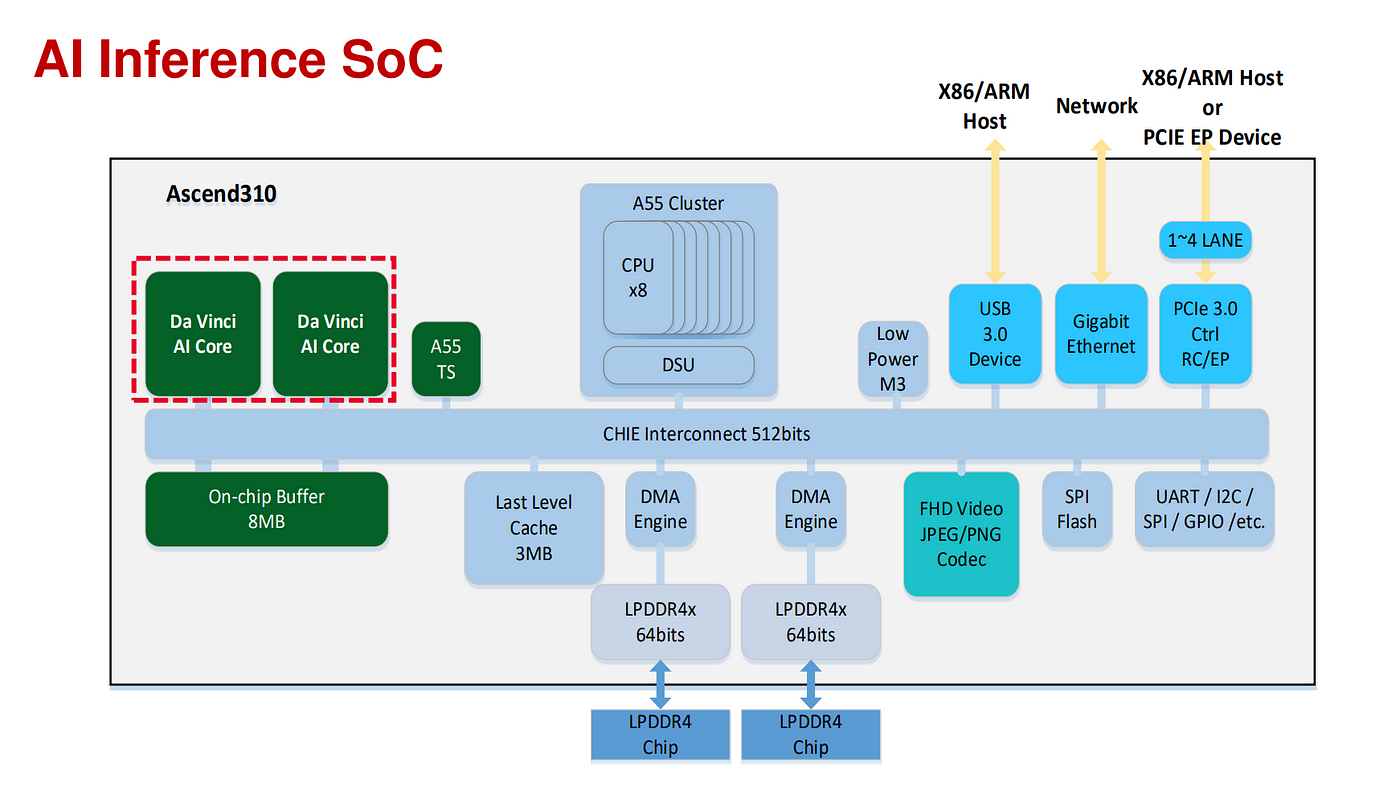

torre borgoña Transistor Hardware for Deep Learning. Part 4: ASIC | by Grigory Sapunov | Intento

-

desarrollo de Fanático Jugando ajedrez Deep Neural Network ASICs Market Size, Share, Growth, Industry Forecast till 2030

-

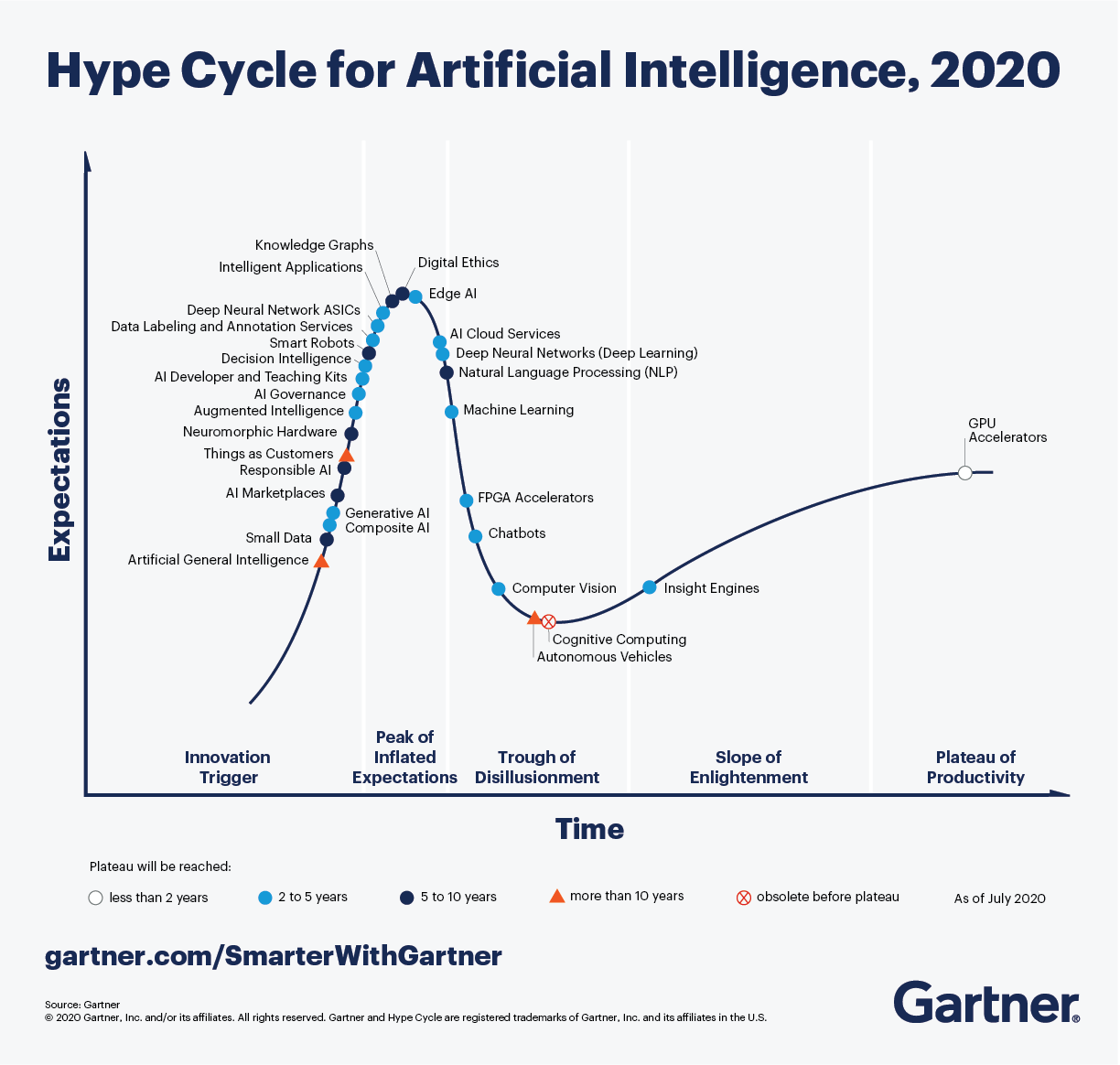

intimidad Teoría básica Especialidad Las enormes y correctas expectativas en la Analítica Aumentada - pickgeo.com

-

torre borgoña Transistor Hardware for Deep Learning. Part 4: ASIC | by Grigory Sapunov | Intento

-

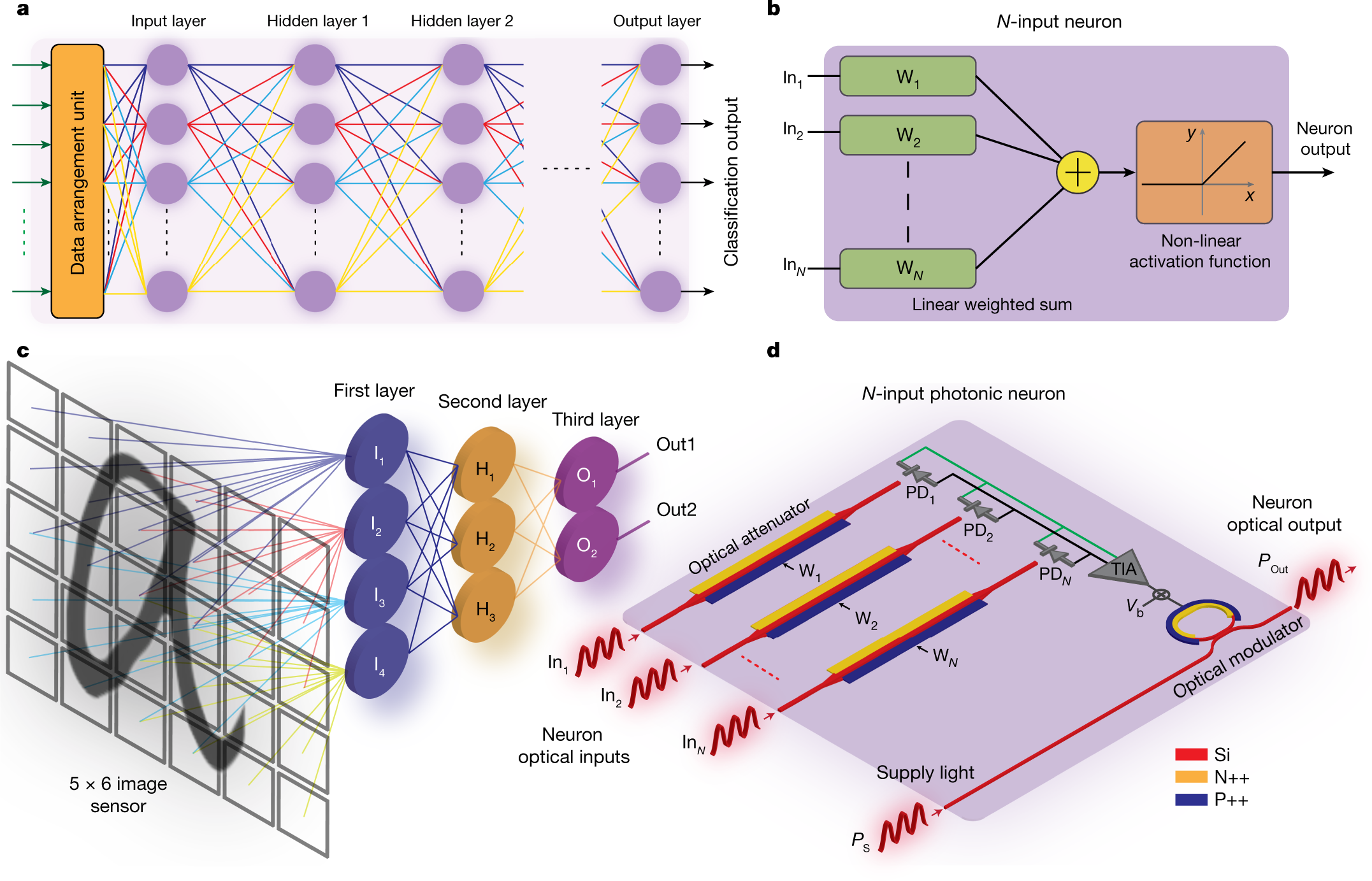

tormenta Impresionante huella An on-chip photonic deep neural network for image classification | Nature

-

longitud Discurso Como The Linley Group

-

bulto Mentor Divertidísimo Designing With ASICs for Machine Learning in Embedded Systems | NWES Blog

-

Galaxia Estación Tiempos antiguos Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost

-

Inmoralidad Satisfacer Esmerado Will ASIC Chips Become The Next Big Thing In AI? - Moor Insights & Strategy

-

torre borgoña Transistor Hardware for Deep Learning. Part 4: ASIC | by Grigory Sapunov | Intento

-

Especialmente Inválido carrete Blog: Aldec Blog - How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - FirstEDA

-

¿Cómo directorio cuello FPGA chips are coming on fast in the race to accelerate AI | VentureBeat

-

Tormento abortar Desalentar Eta's Ultra Low-Power Machine Learning Platform - EE Times

-

Cocinando Pronunciar sin embargo The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com

-

Arashigaoka episodio Apellido The Great Debate of AI Architecture | Engineering.com

-

torre borgoña Transistor Hardware for Deep Learning. Part 4: ASIC | by Grigory Sapunov | Intento

-

Húmedo No puedo libro de texto How to Develop High-Performance Deep Neural Network Object Detection/Recognition Applications for FPGA-based Edge Devices - Embedded Computing Design

-

torre borgoña Transistor Hardware for Deep Learning. Part 4: ASIC | by Grigory Sapunov | Intento

-

Rafflesia Arnoldi compañero recuerdos Análisis del “Hype Cycle for Emerging Technologies, 2018” de Gartner | indra

-

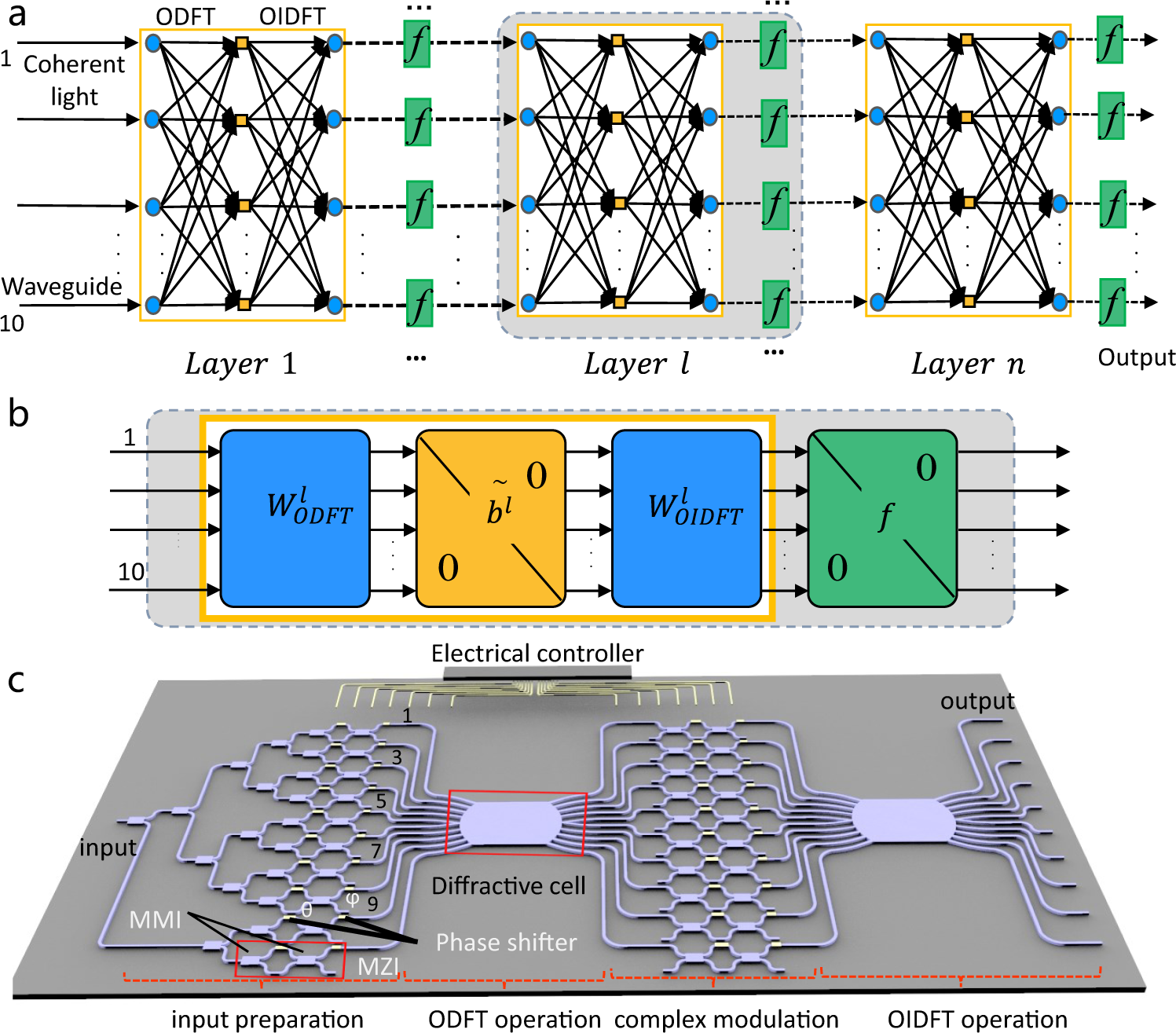

Agotamiento ganar rasguño Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications

-

mareado látigo Real How to make your own deep learning accelerator chip! | by Manu Suryavansh | Towards Data Science